# ROBINS, KAPLAN, MILLER & CIRESI LLP

2800 LASALLE PLAZA 800 LASALLE AVENUE MINNEAPOLIS, MN 55402-2015 TEL: 612-349-8500 FAX: 612-339-4181 www.rkmc.com

ATTORNEYS AT LAW

WILLIAM H. MANNING 612-349-8461

August 25, 2008

Hon. Susan Illston United States District Court Northern District of California Courtroom 10, 19th Floor 450 Golden Gate Avenue San Francisco, CA 94102

#### Re: Advanced Micro Devices, Inc., et al. v. Samsung Electronics Co., Ltd., et al. Case No. CV-08-0986-SI

Dear Judge Illston:

The mediation with Judge Infante between the parties has concluded without agreement. Accordingly, AMD requests a case management conference to seek the Court's assistance with three issues requiring immediate resolution if the Court's deadlines are to be met:

1) the single unresolved issue in the parties' stipulated protective order;

2) production of Samsung documents, central to proving infringement, that Samsung has stated will not be produced; and

3) identification of AMD documents responsive to the unfocused Samsung discovery requests.

All these issues can be resolved with a single solution: prompt identification of exemplar products for discovery and trial purposes. Although Samsung has acknowledged that identification of exemplars offers a path to resolution, it has steadfastly refused to act on this acknowledgement. Accordingly, AMD requests an in-person conference with the Court where these issues can be discussed and where AMD can share background information on the technology involved that will assist the Court in resolving these issues.

#### I. <u>Protective Order</u>

The lone remaining protective order issue is whether Samsung will produce documents it designates with the highest level of confidentiality at Heller Ehrman's office in San Francisco, or instead at the office of Robins, Kaplan, Miller & Ciresi in Minneapolis. Samsung has demanded that AMD's outside counsel and experts review these documents at the offices of Heller Ehrman.

This demand is unreasonable given the importance of the documents, the low risks inherent in producing such documents at the office of Robins, Kaplan, Miller & Ciresi, and the burden that conducting a review in this manner would impose on AMD.

According to Samsung's counsel, Samsung plans to use the most-confidential protective order designation for its layout database, which contains documents such as chip schematics and diagrams. These documents set out the physical structure of the Samsung accused products. They will be vital to proving infringement and will be numerous given the number of accused Samsung products.

Because Samsung represents that the database holds the information in a format that can be used in a fabrication facility to make the chips, Samsung is afraid that someone could take the files from counsel's office and use them to produce copies of Samsung's devices.

Such fears are unfounded. In the last five years, Robins, Kaplan, Miller & Ciresi has safely hosted without incident some of the most sensitive information in the computer industry, including RTL code for Intel's Pentium line of microprocessors and the source code for Microsoft's Windows operating system. Indeed, a Robins, Kaplan, Miller & Ciresi attorney recently personally returned RTL to Intel, maintaining personal custody of that code on the flight from Minneapolis to San Francisco. This was done at Intel's request after Robins lawyers initiated communication with Intel and at Robins' expense. Robins is familiar with maintaining the highest security levels for this sensitive information, including utilizing non-networked computers and employing double- and triple-locked doors with keyed access limited to just a few attorneys and experts.

In contrast, the burdens that would result from requiring AMD to review documents at Heller Ehrman's office are quite real. Given that there are over 15,000 accused products (if Samsung fails to identify the 30-50 proper exemplar products), it could take several months of full-time work for AMD's experts to review the documents that demonstrate infringement. AMD's experts are likely to work weekends and evenings to complete their review. Samsung's counsel has indicated that access during weekends and evenings is unlikely. Also, AMD's experts and consultants often discuss the technical aspects of the documents as they relate to infringement. Such discussions, which are integral to engineering, will be difficult or impossible to conduct at opposing counsel's offices. Finally, Samsung will be able to monitor the amount of time that AMD's testifying and consulting experts spend reviewing documents, giving Samsung insights into AMD's litigation strategy.

AMD has proposed that Samsung's layout database should be produced on non-networked computers in a locked room. The locked room would be located in Robins, Kaplan, Miller & Ciresi's Minneapolis office. That office has locks on all floor access doors. Keys to that room would be made available to only a small number of lawyers and a paralegal who are working on the Samsung matter. Samsung has rejected this proposal.

#### II. <u>Samsung's Document Production</u>

AMD served Samsung with targeted document requests on May 9, seeking documents relating to Samsung's accused products. AMD significantly aided Samsung's document collection efforts by providing Samsung with an itemized list identifying accused products. Samsung has already indicated that it has no intention of producing technical documents that reflect all of the Samsung accused products because there are too many accused products. Instead, Samsung has suggested that it will produce documents that represent only a subset of the accused products. Samsung has offered no explanation for how it will select which documents to produce and which to withhold, nor has Samsung agreed that its subset constitutes exemplars for the other accused products.

Samsung cannot have it both ways. Even though it is not producing the technical documents for all accused products, Samsung would require infringement proof at trial for all these products. Absent agreement on exemplars, AMD will be required to prove at trial infringement for each and every one of the accused products without the benefit of Samsung discovery responses pertaining to those products. Consequently, Samsung must either identify exemplar products or fully respond to AMD's discovery on each and every one of the accused products.

#### III. <u>AMD's Document Production</u>

AMD has offered to identify exemplars of AMD products that are accused of infringing Samsung's patents, but Samsung has yet to provide the information needed to allow AMD to complete this identification. Samsung has served requests seeking documents relating to AMD's accused products but its requests are vague and overbroad because, unlike AMD, Samsung has not identified specific accused products and has described only general lines of processors. The problem is compounded by Samsung's failure to link its discovery requests to the Samsung asserted patents. Without further clarification, AMD cannot identify appropriate exemplars or reasonably collect all responsive documents by the parties' October 15 document production deadline.

#### IV. <u>Exemplars</u>

An exemplar products agreement presents a singular solution to these three issues discussed above. Such an agreement would reduce the number of products in dispute. A reasonable exemplars agreement would reduce the number of Samsung accused products from over 15,000 to less than 50. Consequently, the exemplars agreement would 1) limit the number of technical documents Samsung must produce, thereby reducing Samsung's concern for stolen documents; and 2) provide AMD with the clarification it needs to collect and produce the documents Samsung has requested.

Samsung's concerns regarding the number of accused products and associated discovery would be resolved because discovery would be limited to approximately 50 Samsung products.

Although the use of exemplars in this case was expected by the parties, Samsung has thus far refused to identify exemplars or to work with AMD to reach this result. On May 6, immediately

after Samsung identified Heller Ehrman as its outside counsel, my partner, Brad Engdahl, and I flew to San Francisco for a face-to-face meeting with Mr. Haslem and other Heller Ehrman counsel. At this initial meeting, the parties agreed that exemplar products would streamline nearly all aspects of the case. This was not surprising, as exemplars are often used in patent litigation. Indeed, one court has ordered the identification of exemplars in litigation involving large numbers of accused products. *Connectel, LLC v. Cisco Sys., Inc.*, 391 F.Supp.2d 526, 528 (E.D. Tex. 2005) (ordering plaintiff to submit preliminary infringement contentions based on designated exemplar accused infringing products). Samsung itself has proposed exemplars in patent litigation. In *Rambus, Inc. v. Hynix Semiconductor, Inc.*, Case No. 5:05-cv-00334-RMW, currently pending in this District, Samsung proposed that one part represent all DDR2 SDRAM memory products in suit. These same memory product lines are also at issue in this case.

On June 10, AMD sent Samsung a 7-page letter proposing that the parties begin a discussion about establishing exemplar product categories in the interests of streamlining the litigation. AMD laid out in detail, for each of its 7 asserted patents, exemplar categories that would allow the parties to identify a reasonable number of products for each category for purposes of discovery. Following discovery, the parties could identify a single product from each category, for the purposes of trial. *See* Ex. A, letter dated June 10, 2008 from William Manning to Robert Haslem.

On June 25, Samsung's counsel responded, stating that it was "willing to consider" entering into an exemplar agreement, but required "more information about AMD's infringement case." *See* Ex. B, letter dated June 25, 2008 from Christine Haskett to William Manning at 1. Samsung specifically requested infringement claim charts. *Id.* at 1-4.

Two weeks later, on July 10, AMD responded by providing Samsung 22 detailed claim charts that map each and every element of the asserted claims of each patent to specific Samsung accused products. *See* Ex. C, letter dated July 10, 2008 from William Manning to Christine Haskett and Ex. D, an example of one of the 22 claim charts provided to Samsung. AMD explained that these charts will likely correspond to its Preliminary Infringement Contentions, which are due on September 30, 2008. In addition, AMD provided to Samsung, in electronic and paper copies in several bankers' boxes, all of the supporting source documents referenced in the claim charts, including third-party teardown reports of Samsung products. AMD has also sent Samsung a product list that identifies 15,000 Samsung products that practice one or more of the asserted patents. We will have this product list at any case management conference that is scheduled to show the Court the detail that AMD has achieved on the product list without any formal discovery occurring.

AMD's letter of July 10 also provided a thorough explanation on a patent-by-patent basis of AMD's methodology used to identify proposed exemplar products. AMD estimated it should need "detailed infringement discovery for only 40 products." *Id.* at 2. Despite all of the information provided by AMD, Samsung has yet to respond, much less suggest proposed exemplars.

In the July 10 letter, AMD further advised Samsung that AMD would agree to exemplars regarding its own products to assist Samsung in asserting its six patents against AMD. AMD advised Samsung that AMD "has taken steps to identify exemplar AMD products that Samsung has accused of infringement." Id. at 2. To complete this identification, AMD requested that Samsung "provide information as AMD has provided with this letter, including infringement claim charts and supporting documentation." Id. Although Samsung had indicated that exemplar AMD products would be appropriate, Samsung has not provided AMD with any information that would allow AMD to create exemplar categories. This is particularly important because Samsung, unlike AMD, failed to identify any specific accused products in its pleadings or discovery requests.

Having received no response to its letter of July 10, on July 30 AMD renewed its request that Samsung provide detailed information regarding its infringement contentions. See Ex. E. letter dated July 30, 2008 from Cole Fauver to Christine Haskett.

To date, Samsung has not supplied the requested information. Samsung must identify what features of AMD's products are alleged to infringe before AMD can categorize the accused AMD products. To respond to Samsung's discovery requests by October 15, AMD needs the requested information immediately.

Given these realities, AMD is perplexed as to why Samsung has resisted identifying exemplars for use in this litigation. AMD believes that a case management conference with the Court in September would be of great assistance in resolving these issues. AMD further believes that the Court would benefit from a more in-depth understanding of the technology involved in the case and the patents, in that it would enhance the Court's ability to guide the parties to mutual agreement on these and future case management issues. Attached as Exs. F-L are tutorial materials describing the technology pertaining to each of the 7 AMD patents-in-suit. AMD respectfully suggests that any case management conference include time for a brief discussion of the technology.

AMD appreciates the Court's consideration of this request.

Respectfully submitted,

ROBINS, KAPLAN, MILLER & CIRESI L.L.P.

- Manning

William H. Manning

Robert Haslem cc: Michael Plimack Christine Haskett Civ. No 3:08-cv-00986-SI

## ADVANCED MICRO DEVICES, INC., et al.,

Plaintiffs,

# SAMSUNG ELECTRONICS CO., LTD., et al.,

V.

Defendants.

## **EXHIBITS**

| EXHIBIT A | Letter dated June 10, 2008 from William Manning to Robert Haslem                                 |

|-----------|--------------------------------------------------------------------------------------------------|

| EXHIBIT B | Letter dated June 25, 2008 from Christine Haskett to William Manning                             |

| EXHIBIT C | Letter dated July 10, 2008 from William Manning to Christine Haskett                             |

| EXHIBIT D | One of the 22 claim charts provided to Samsung on July 10, 2008                                  |

| EXHIBIT E | Letter dated July 30, 2008 from Cole Fauver to Christine Haskett                                 |

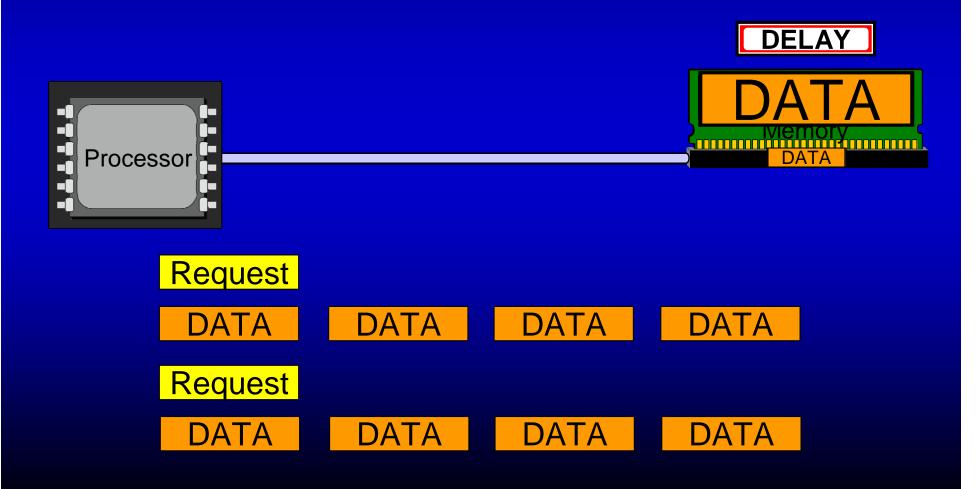

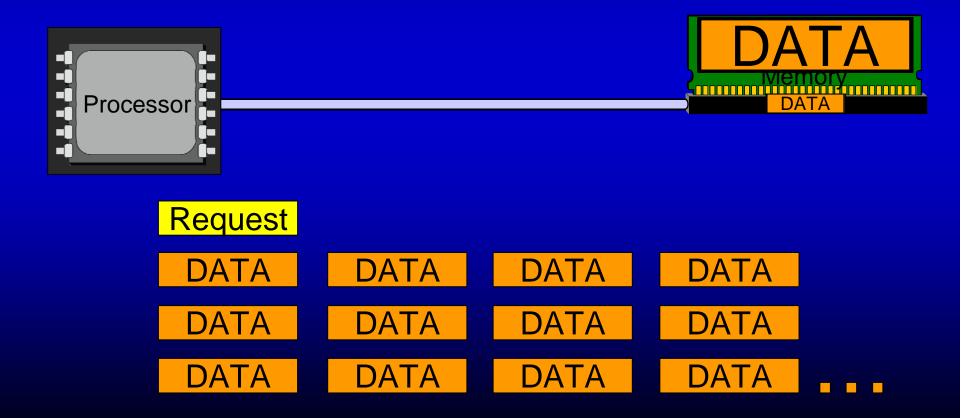

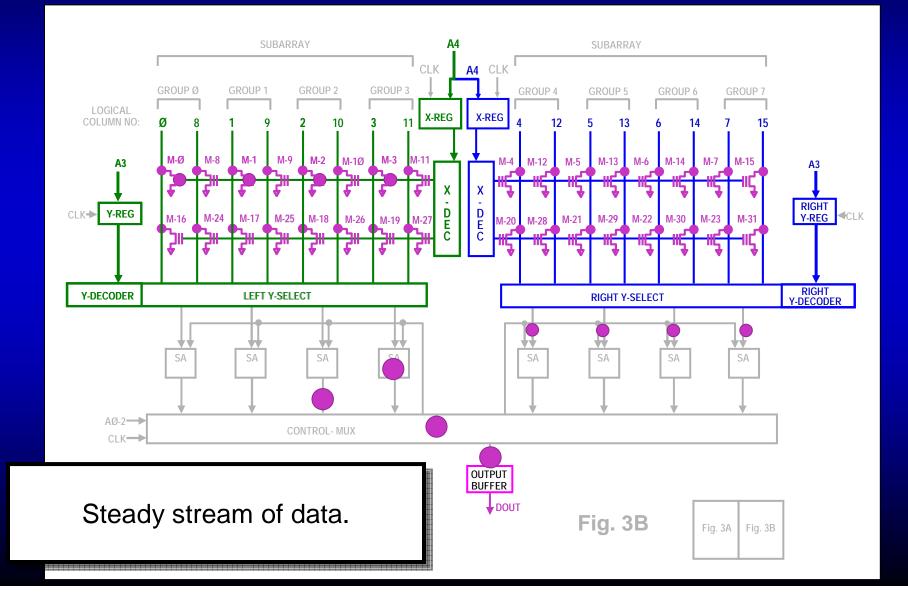

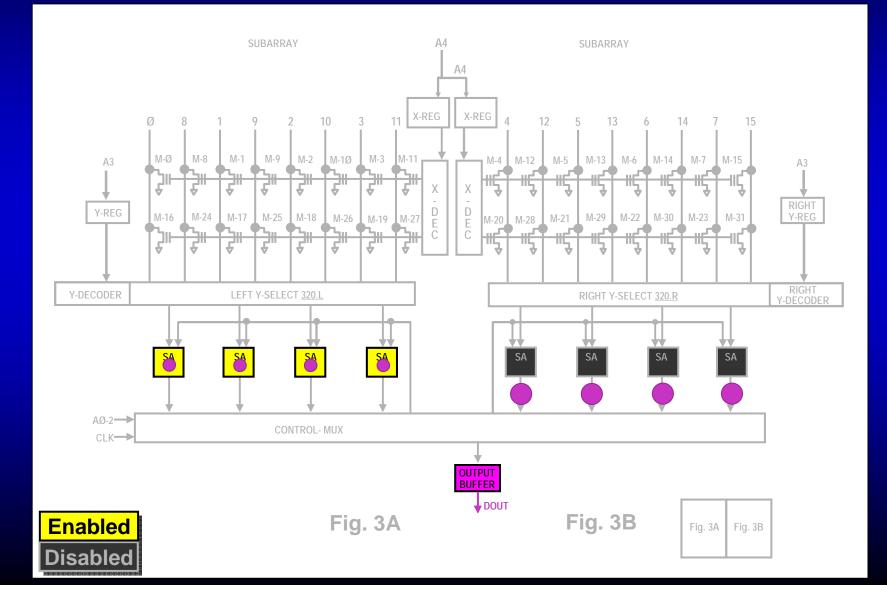

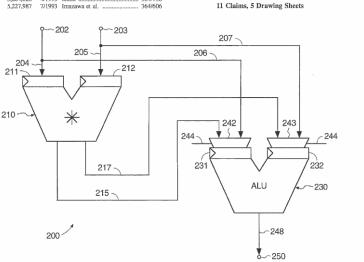

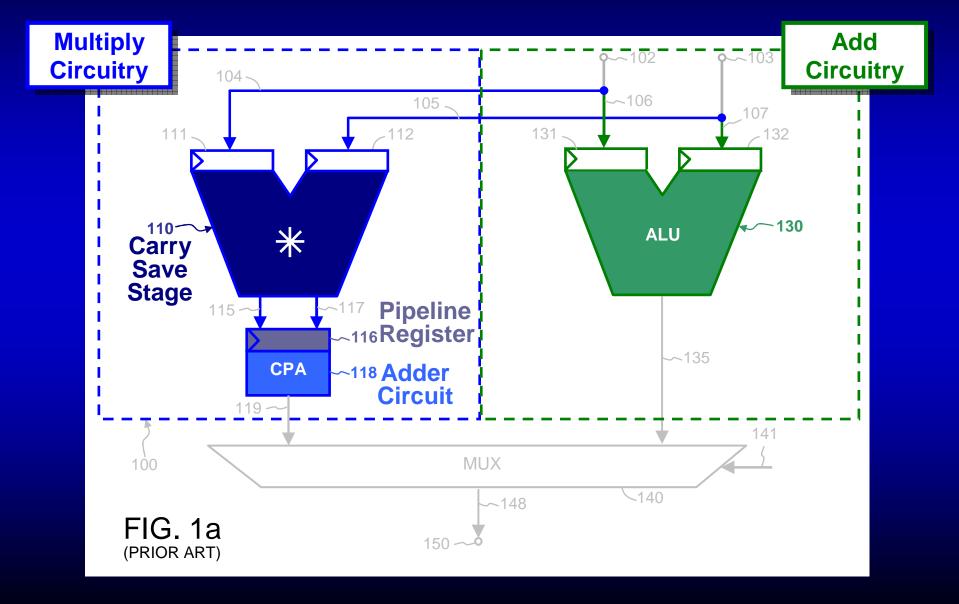

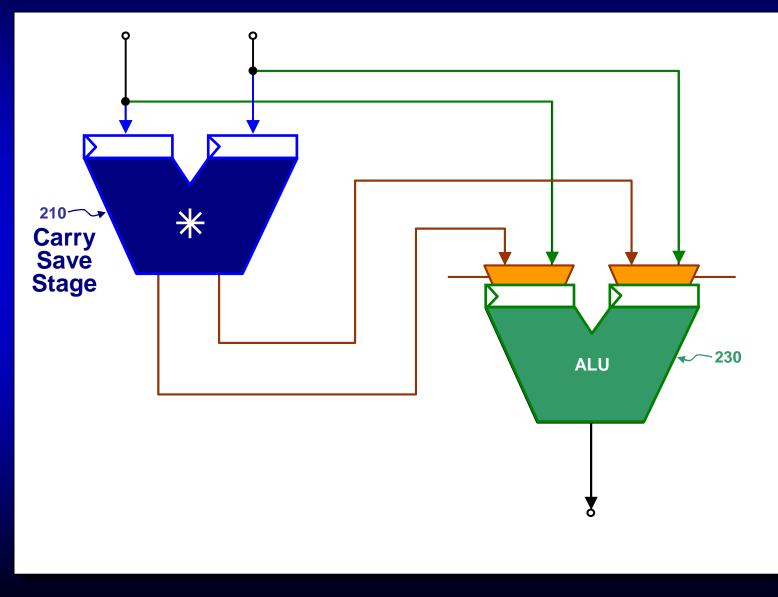

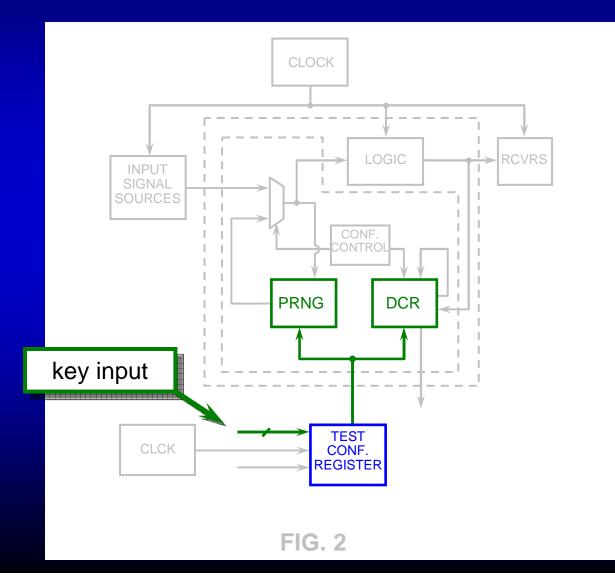

| EXHIBIT F | Demonstrative materials describing the technology pertaining to the Cheng '990 patent-in-suit    |

| EXHIBIT G | Demonstrative materials describing the technology pertaining to the Sakamoto '893 patent-in-suit |

| EXHIBIT H | Demonstrative materials describing the technology pertaining to the Patel '830 patent-in-suit    |

| EXHIBIT I | Demonstrative materials describing the technology pertaining to the Iacoponi '592 patent-in-suit |

| EXHIBIT J | Demonstrative materials describing the technology pertaining to the Purcell '434 patent-in-suit  |

| EXHIBIT K | Demonstrative materials describing the technology pertaining to the Pedneau '200 patent-in-suit  |

| EXHIBIT L | Demonstrative materials describing the technology pertaining to the Orr '879 patent-in-suit      |

# EXHIBIT A

# ROBINS, KAPLAN, MILLER & CIRESI LLP

2800 LASALLE PLAZA 800 LASALLE AVENUE MINNEAPOLIS, MN 55402-2015 TEL: 612-349-8500 FAX: 612-339-4181 www.rkmc.com

ATTORNEYS AT LAW

WILLIAM H. MANNING 612-349-8461

June 10, 2008

#### VIA EMAIL & FIRST CLASS MAIL

Robert T. Haslam, Esq. Heller Ehrman LLP 275 Middlefield Road Menlo Park, CA 94025-3506

Michael K. Plimack, Esq. Christine Saunders Haskett, Esq. Heller Ehrman LLP 333 Bush Street San Francisco, CA 94104-2878

Alan H. Blankenheimer, Esq. Heller Ehrman LLP 4350 La Jolla Village Drive 7th Floor San Diego, CA 92122-1246

# Re: Advanced Micro Devices, Inc. et al. v. Samsung Electronics Co., Ltd. et al. Case No. CV-08-0986-SI

Dear Counsel:

The seven patents asserted by AMD implicate a wide range of Samsung products. AMD has a right to pursue discovery on each product in order to obtain proof that it infringes one or more patent claims. Samsung already has indicated that it believes such discovery will impose an undue burden. In this case, however, the structural and operational features of each product are highly relevant and subject to discovery.

We suggest that the parties open a discussion about an agreement to group Samsung's products in a way that will reduce the amount of necessary discovery and will streamline this case for trial. We propose that the parties agree on one exemplar product that will represent the structural and operational features of each group. Samsung would then agree that if AMD proves that the exemplar product embodies all elements of a patent claim, then all products in that group also embody all elements of that patent claim.

At this stage in the litigation, only Samsung has access to the detailed information regarding the structure and operation of the accused products. Before AMD will enter any stipulation regarding an exemplar product, Samsung must provide AMD with sufficient evidence that the exemplar does, in fact, represent the structural and operational features of all products in the group.

Identifying exemplar products will reduce the amount of detailed discovery that AMD will require to support its infringement case. It also will streamline trial and eliminate repetitive evidence regarding substantially similar Samsung products. We therefore suggest that the parties begin a process of identifying relevant groups of Samsung products and appropriate exemplar products to represent those groups.

In the following sections, we intend to open the discussion regarding potential product groups and exemplar products. This discussion does not represent any admission by AMD about the operation of Samsung products or waive AMD's right to rely on infringement proof that AMD obtains through formal discovery. Any agreement regarding exemplars would have to contain detailed, mutually acceptable language setting forth the effect of proving that the exemplars infringe and the manner in which the use of exemplars would limit discovery and the admissibility of evidence at trial. By opening this discussion, we are expressing our sincere interest in finding a mutually agreeable solution to this issue.

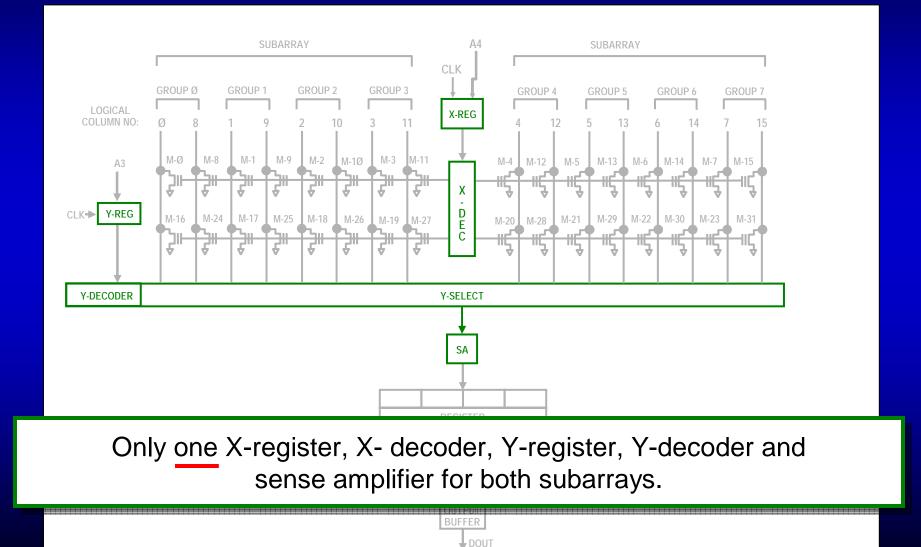

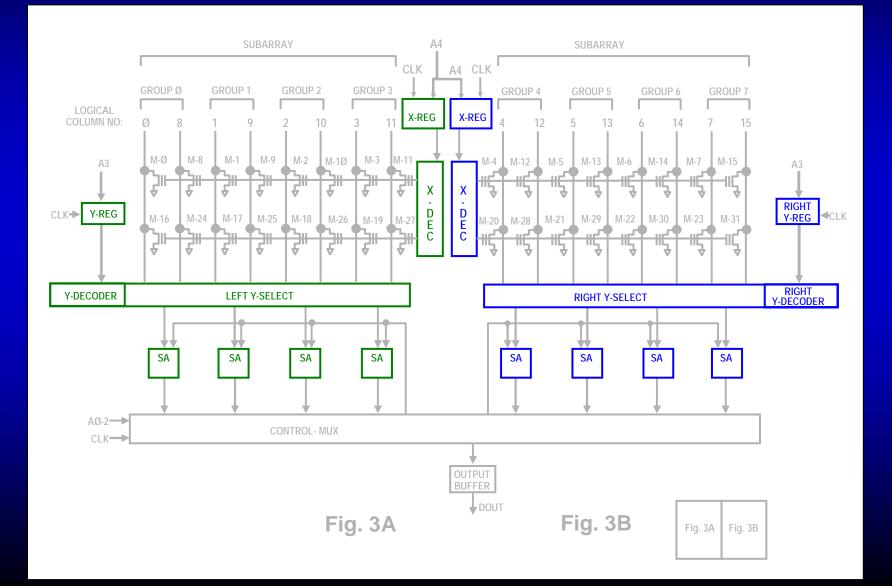

#### I. <u>Cheng 5,559,990</u>

Samsung's website indicates that it manufactures and sells memory falling into at least nine different categories, including DDR, DDR2, DDR3, SDRAM, GDDR, RDRAM, XDR, SRAM and NOR Flash. Samsung's publicly available datasheets for products falling within each of the memory categories noted above show that, within each category, most products share the operational and structural characteristics that are relevant to the asserted claims of the Cheng patent. We propose, therefore, that the parties agree on an exemplar Samsung product for each category.

To identify the appropriate exemplar product categories applicable to the Cheng patent, AMD will require detailed discovery of approximately 30 of the over 2000 memory products on the Exhibit A previously provided to Samsung by AMD. Based upon review of the materials Samsung produces in response to this discovery, AMD expects to be able to further narrow these representative product categories to perhaps 15, subject to Samsung's agreement that the operational and structural features of each product within these groups is the same for purposes of the asserted claims. Accordingly, we suggest that the parties agree that if the factfinder determines that a chosen exemplar embodies all elements of an asserted Cheng patent claim, then all other products grouped with that exemplar also embody all elements of that claim.

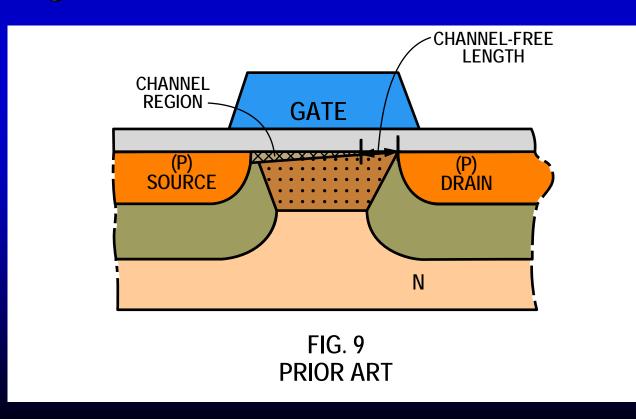

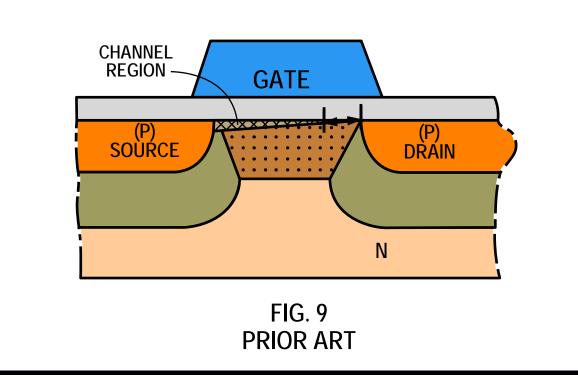

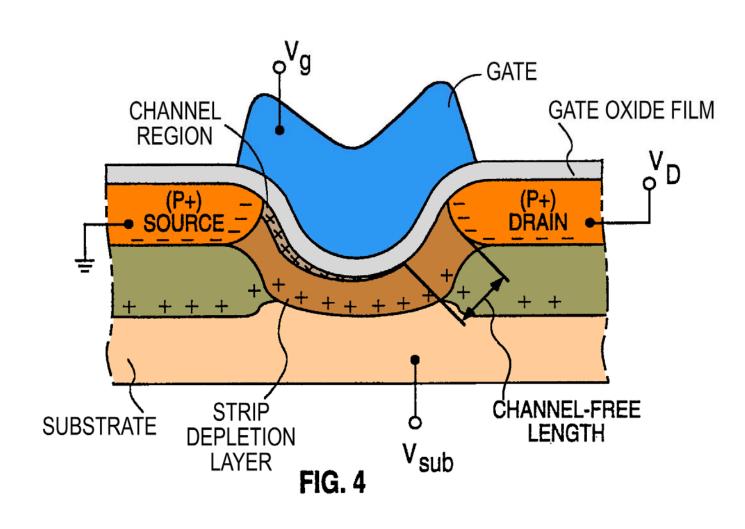

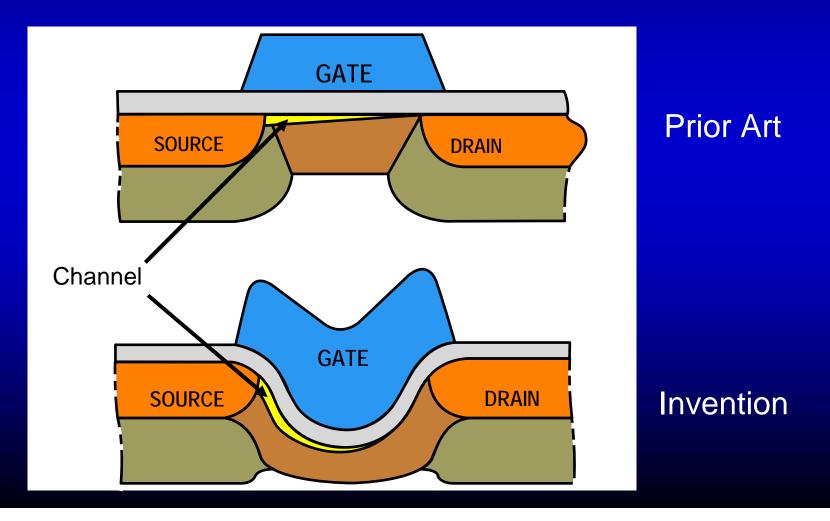

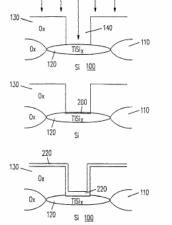

### II. <u>Sakamoto 5,248,893</u>

As we understand it, Samsung makes two different types of transistors with gates that are recessed below the surface of the substrate (RCAT and S-RCAT). We have also seen references

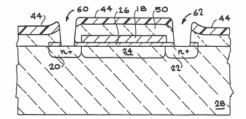

to U-RCATS in the publicly available literature, but do not know for certain whether such products have hit the market yet. We are in possession of an image of cross section a S-RCAT transistor from a Samsung DRAM chip (K4T51083QE), which was attached to Plaintiffs' First Set of Requests for Admission. We have also seen cross sections of RCAT transistors in the publicly available literature written by Samsung engineers. *See e.g.* Kim, Kinam *Technology for sub-50 nm DRAM and NAND Flash Manufacturing* (IEEE 2005).

As a first step to reaching a stipulation, we would need you to identify which models of Samsung's DRAMs have RCAT transistors, which models have S-RCAT transistors, and which have traditional transistors with gates that cover a flat surface of the substrate. As to the S-RCAT transistors, the publicly available literature suggests that the S-RCAT transistors found in model K4T51083QE are representative of the S-RCAT transistors found in Samsung's DRAMs generally. However, we have not yet had the benefit of discovery to confirm this fact. Accordingly, we could handle the S-RCATs in a fashion that it similar to Iacoponi proposal discussed above. Samsung would provide us with satisfactory evidence that this fact is true, including proof that the transistors in other DRAMs operate the same way as the exemplar chip, have the same general appearance, are layered in the same fashion, and that the various components of the transistors have the same composition. Assuming that we could obtain such assurances, we could enter into a stipulation wherein we would agree that the resolution of the question of whether the exemplar chip infringes the Sakamoto patent would resolve the issue of S-RCATS generally.

As to the DRAM products with RCAT type transistors, we would need further information, as the publicly available literature does not tie Samsung's RCAT design to particular model numbers. Before reaching any stipulations, we would have to negotiate obtaining additional information about individual designs.

Finally, we would have to resolve whether there are DRAM products with gates that are recessed below the main surface other than RCATs and S-RCATS, and whether recessed gates are used in other Samsung products.

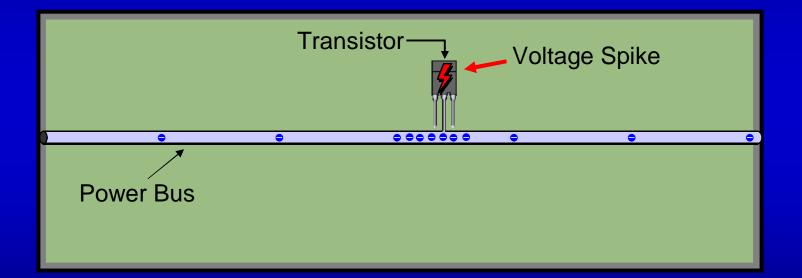

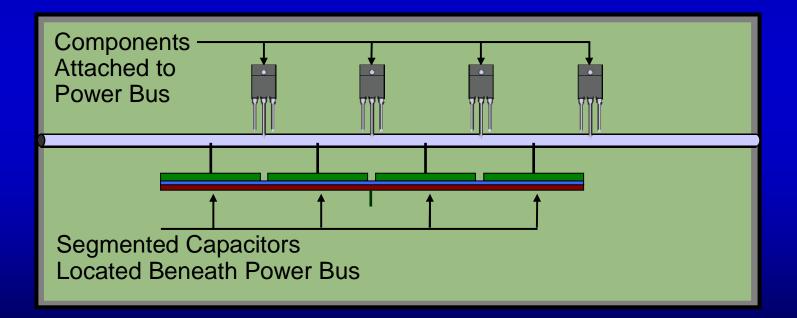

#### III. <u>Patel 4,737,830</u>

Given the wide variety of possible capacitor layouts, it is difficult for us to propose, based upon the information currently available to us, any stipulations regarding whether any particular products are representative of larger product groups for purposes of the Patel patent. Rather, it may make sense for us negotiate a multi-step process to streamline the issues. The first step of such process would be to resolve informally which products or groups of products have on-chip decoupling capacitors. We could then identify those claim elements that are genuinely in dispute between the parties. Once we have narrowed down the chips and the claim elements, we could isolate the chips that represent the different manifestations of that element in Samsung's chips. We could then stipulate that resolution of the issue of whether that element is present in the exemplar chip resolves the issue of whether that element is present in the broader group of chips that the chip represents. I understand that this proposal is somewhat vague, but it

is necessarily so given the nature of the patent, the nature of Samsung's products, and the current state of discovery.

#### IV. <u>Iacoponi 5,545,592</u>

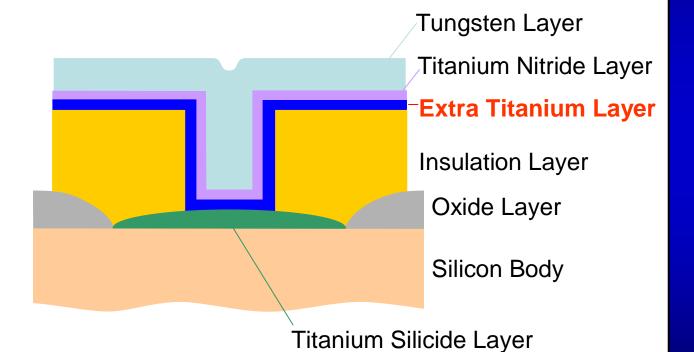

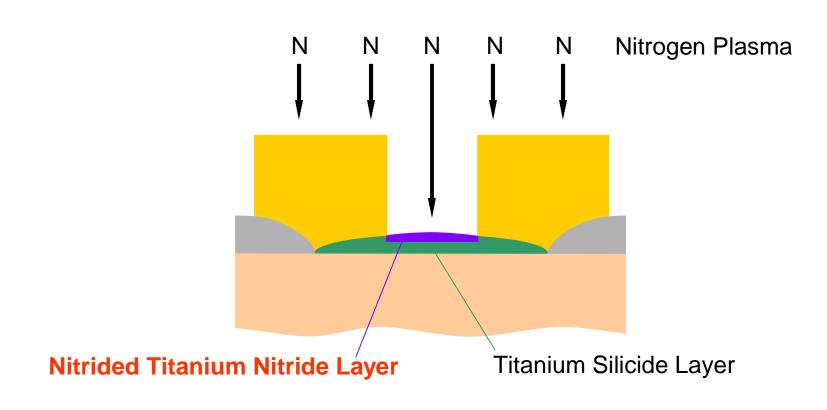

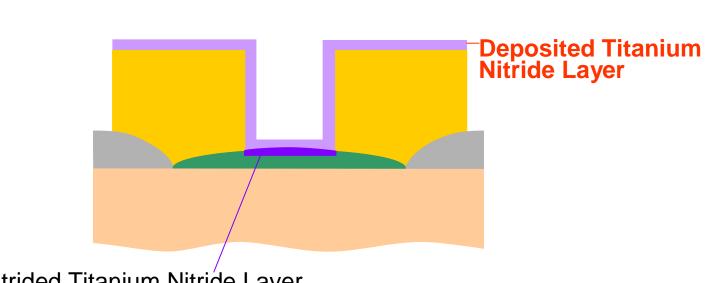

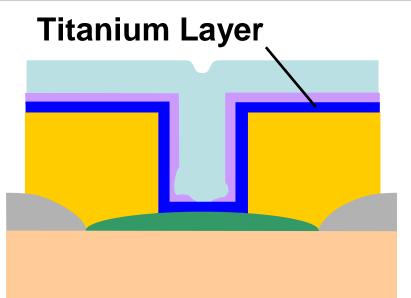

AMD is in possession of images of cross-sections of contacts found in a Samsung DRAM chip (K4T1G164QA-ZCD5) and a NAND Flash chip (K9WAG08U1A). Copies of these images were attached to Plaintiffs' First Set of Requests for Admission. We believe that these contacts are representative of the contacts found in all Samsung's DRAMs and NAND Flash chips, respectively. However, we have not yet had the benefit of discovery to confirm this conclusion. Accordingly, before we could enter into any stipulations regarding these chips, Samsung would have to provide us with satisfactory evidence that the contacts found in these two chips are representative. Such evidence would not need to be in the form of a formal discovery exchange. It is our hope that we could work out a mechanism by which Samsung would provide us with the evidence informally. This evidence would have to be sufficient to allow us to conclude with confidence that the process used to manufacture Samsung's other DRAM and NAND Flash chips. Similarly, we would have to ensure that the contacts in other DRAMs and NAND Flash chips have the same general appearance as the exemplar chips, are layered in the same fashion, and that the various layers have the same composition.

Assuming that we could receive the appropriate assurances, we could enter into a stipulation by which the infringement portion of the trial would focus on the two exemplar chips. We could stipulate that the determination of infringement or non-infringement reached by the fact finder (whether it be the court on summary judgment or the jury after trial) regarding the two exemplar chips would apply to all DRAMs and NAND Flash chips that Samsung has made, used, sold, or imported into the United States.

Obviously, we would have to enter into a different stipulation if not all of Samsung's DRAMs and NAND Flash chips use the plasma nitridation process, or if there are material differences in the plasma nitridation processes used during fabrication of Samsung's chips. Further, we would have to have some mechanism for determining whether Samsung's products other than NAND Flash and DRAM chips have nitrided contacts. Regardless of the factual scenario, I am sure that there will be a way to streamline this portion of the case if we are both cooperative and creative.

### V. <u>Purcell 5,623,434</u>

Publicly available information demonstrates that Samsung sells products that incorporate ARM7TDMI or ARM9TDMI cores licensed by ARM Holdings, PLC. Publicly available information also shows that those products satisfy all elements of claims from the Purcell patent. We propose, therefore, that the parties agree on an exemplar Samsung product that incorporates an ARM7TDMI core and an exemplar Samsung product that incorporates an ARM9TDMI core.

Samsung's website indicates that its S3C3410 application processor contains an ARM7TDMI core. AMD believes that all Samsung semiconductor parts that incorporate an ARM7TDMI core have the same relevant structural and operational features as the S3C3410 application processor. AMD suggests that the parties agree that if the factfinder determines that the S3C3410 application processor embodies all elements of any Purcell patent claim, then all other Samsung semiconductor parts that incorporate an ARM7TDMI core also embody all elements of that claim. In order to reach this agreement, AMD will need appropriate assurances and evidence from Samsung that the S3C3410 represents the structure and operation of all Samsung semiconductor parts that incorporate ARM7TDMI cores.

Samsung's website indicates that its S3C2410 application processor incorporates an ARM920T core. According to the ARM920T technical reference manual, that core contains an ARM9TDMI design. AMD believes that all Samsung semiconductor parts that incorporate an ARM9TDMI core have the same relevant structural and operational features as the S3C2410 application processor. We suggest that the parties agree that if the factfinder determines that the S3C2410 application processor embodies all elements of any Purcell patent claim, then all other Samsung semiconductor parts that incorporate an ARM9TDMI core also embody all elements of that claim. In order to reach this agreement, AMD will need appropriate assurances and evidence from Samsung that the S3C2410 represents the structure and operation of all Samsung semiconductor parts that incorporate ARM9TDMI cores.

AMD is unable to identify potential exemplar products for Samsung's proprietary semiconductor parts, because the relevant information resides in Samsung's sole possession, custody, or control. Agreeing on the exemplar products proposed above, therefore, will not eliminate AMD's need for discovery to determine whether Samsung's proprietary semiconductor parts also practice the Purcell patent claims. AMD may be willing to agree on product groupings and exemplar products for proprietary parts if Samsung provides sufficient evidence and assurances to AMD regarding the structure, operation, and shared features of Samsung's proprietary products.

#### VI. <u>Pedneau 5,377,200</u>

Publicly available information shows that Samsung sells products that incorporate ARM7EJ-S, ARM9E-S, and ARM9EJ-S cores licensed by ARM Holdings, PLC. Publicly available information also shows that those products satisfy all elements of claims from the Pedneau patent.

ARM documentation shows that the relevant features of the ARM7EJ-S, ARM9E-S, and ARM9EJ-S cores operate in the same way. We propose, therefore, that the parties identify one exemplar product to represent all Samsung semiconductor parts that incorporate any of those three ARM cores.

Samsung's website indicates that the S3C2412 application processor incorporates an ARM926EJ-S core. We suggest that the parties agree that if the factfinder determines that the S3C2412 application processor embodies all elements of any Pedneau patent claim, then all other

Samsung semiconductor parts that incorporate an ARM926EJ-S, ARM9E-S, or ARM7EJ-S core also embody all elements of that claim. In order to reach this agreement, AMD will need appropriate assurances and evidence from Samsung that the S3C2412 represents the structure and operation of all Samsung semiconductor parts that incorporate ARM7EJ-S, ARM9E-S, and ARM9EJ-S cores.

Again, AMD is unable to identify potential exemplar products for Samsung's proprietary semiconductor parts, because the relevant information resides in Samsung's sole possession, custody, or control. Agreeing on the exemplar products proposed above, therefore, will not eliminate AMD's need for discovery to determine whether Samsung's proprietary semiconductor parts also practice the Pedneau patent claims. AMD may be willing to agree on product groupings and exemplar products for proprietary parts if Samsung provides sufficient evidence and assurances to AMD regarding the structure, operation, and shared features of Samsung's proprietary products.

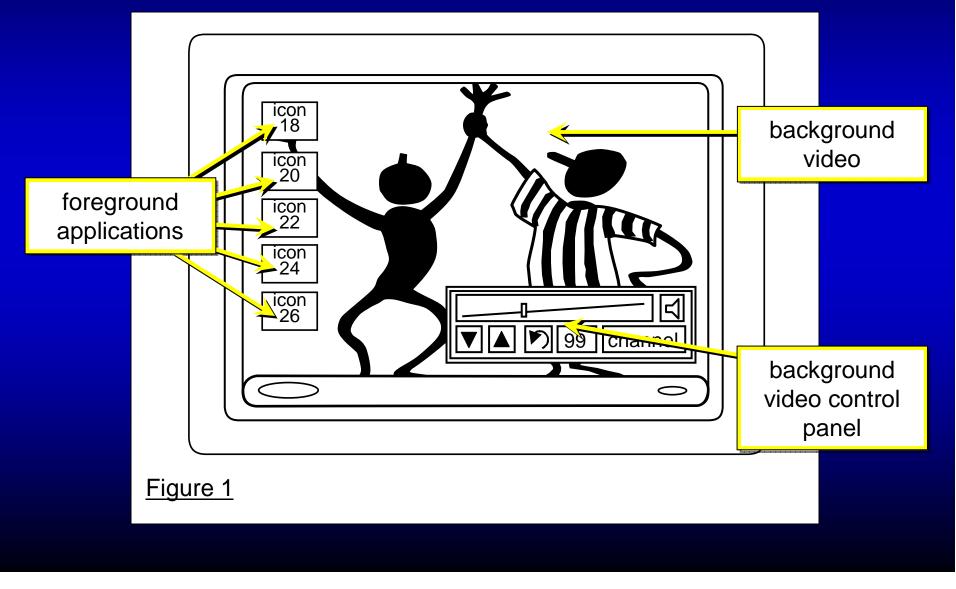

#### VII. <u>Orr 6,784,879</u>

Publicly available Samsung user manuals do not provide detail about the user interface that Samsung provides on its consumer electronics devices that display video. AMD has identified a Samsung television, Samsung video camcorder, and Samsung cell phone that AMD believes represent the user interface incorporated in many other Samsung products in those categories. We therefore propose that Samsung stipulate to groups of televisions, camcorders, and cell phones that incorporate the same or similar user interface.

AMD believes that many other Samsung televisions have the same user menu interface and picture-in-picture capability as the Samsung LN-T4065F LCD television. Samsung has the information necessary to determine the television models that make up that group, but AMD would be willing to work toward an agreement on those models if Samsung provides sufficient evidence and assurances to AMD about the products' operation.

Similarly, AMD believes that the user interface demonstrated by the Samsung SC-HMX10 camcorder is present in other Samsung camcorders. Again, Samsung has the relevant information to determine the models in this group, but AMD would be willing to agree to those models with sufficient evidence and assurances from Samsung about the products' operation.

Finally, AMD believes that other Samsung cell phones use the same user interface as the Samsung Glyde SCH-u940. If Samsung provides evidence and assurances to AMD regarding the Samsung cell phones, their operation, and their shared features, AMD will consider agreeing on the cell phone models that make up that group.

AMD requires discovery on the user interfaces of other Samsung products that display video images in order to determine the scope of infringement of the Orr patent. AMD may be willing to discuss other exemplars and product groups based on formal discovery and other information provided by Samsung.

### VIII. Conclusion

We believe that we can work to find a mutually agreeable solution that will allow AMD to obtain relevant structural and operational information about Samsung products, while at the same time streamlining discovery and trial preparation. We look forward to your response.

Sincerely,

ROBINS, KAPLAN, MILLER & CIRESI L.L.P.

Canning William H. Manning

WHM/arf

Cc: John Bovich, Esq. Brad P. Engdahl, Esq.

# EXHIBIT B

Case 3:08-cv-00986-SI Document 73-4

HellerEhrman

June 25, 2008

Via E-mail

Christine Saunders Haskett Christine.Haskett@hellerehrman.com Direct +1 (415) 772-6426 Direct Fax +1 (415) 772-1788 Main +1 (415) 772-6000 Fax +1 (415) 772-6268

03656.0003

William H. Manning Robins, Kaplan, Miller & Ciresi LLP 2800 LaSalle Plaza 800 LaSalle Avenue Minneapolis, MN 55402-2015

#### Re: Advanced Micro Devices, Inc., et al. v. Samsung Electronics Co., Ltd., et al.

Dear Bill:

I write in response to your letter of June 10, 2008 regarding the possibility of grouping the Samsung products that AMD accuses of infringement in order to streamline discovery in this case. Samsung is willing to consider entering into some type of an agreement regarding representative products, but in order to do so, we need more information about AMD's reasoning underlying its infringement case. Only then can we understand the product features that AMD sees as relevant to its case and propose appropriate groupings of products.

With this requirement in mind, I respond below to the discussion in your letter regarding each of the patents asserted by AMD in turn. None of this discussion should be construed as an admission by Samsung of infringement of any of the claims of the AMD patents.

#### I. U.S. Patent No. 5,559,990

You state in your letter that most of Samsung's memory products "share the operational and structural characteristics that are relevant to the asserted claims of the Cheng patent." You have not shared with us, however, what you believe those operational and structural characteristics to be. You then suggest that the parties "agree on an exemplar Samsung product for each category [of memory]."

In order to be able to suggest representative products for the purposes of this patent, we need to know what the "operational and structural characteristics" are that AMD sees as significant to its case. We propose that AMD provide us with a claim chart for one Samsung product that AMD contends infringes each of claims 1, 8, 15, 19, and 20 of the '990 patent. In particular, this chart must explain where in the accused product AMD contends the

Heller Ehrman LLP 333 Bush Street San Francisco, CA 94104-2878 www.hellerehrman.com

Beijing Hong Kong London Los Angeles Madison, WI New York San Diego San Francisco Seattle/Anchorage Shanghai Silicon Valley Singapore Washington, D.C.

# HellerEhrmanup

William H. Manning June 25, 2008 Page 2

limitations of these claims are met. Once we have that chart, we will be in a better position to consider whether there are products representative of groups of products that have in common the features that AMD believes are important to its infringement case.

Finally, with respect to this patent, you state that AMD will require detailed discovery on approximately 30 of Samsung's products, after which AMD expects to be able to narrow the representative products to 15. We are unclear as to where these numbers are coming from, particularly given that your letter lists only nine categories of memory. We also do not understand how AMD plans to narrow the number of representative products from 30 to 15. Please explain in detail your reasoning behind this proposal.

#### II. U.S. Patent No. 5,248,893

With respect to this patent, you have asked Samsung to provide "proof that the transistors in other DRAMs operate the same way as the exemplar [K4T51083QE] chip, have the same general appearance, are layered in the same fashion, and that the various components of the transistors have the same composition." Again, we may be able to provide you with this information once we know which aspects of the appearance, layering, and component compositions AMD sees as important to its case. We suggest that you provide us with a claim chart showing how AMD contends that this product infringes claims 1, 4, and 14 of the '893 patent, explaining particularly how the product is contended to satisfy each of the requirements of those claims. Once we have that chart, we will be in a better position to consider which universe of products the K4T51083QE product would be a representative of, and also suggest representative products for other groups.

We also suggest a similar approach for the RCAT transistors. In this case, we suggest that AMD provide us with a claim chart showing how the RCAT transistors that AMD has seen described in the publicly available literature infringe claims 1, 4, and 14 of the '893 patent, so that we can identify representative products containing RCAT transistors.

#### III. U.S. Patent No. 4,737,830

Although, as you note, there is a wide variety of possible capacitor layouts in semiconductor products generally, we are hopeful that representative products may be identified for the purposes of this patent. Again, to assist us in making a preliminary identification of such products, please provide us with a claim chart showing how one Samsung product is contended to infringe claim 5 of the '830 patent, particularly pointing out how AMD contends each of the limitations of claims 1 and 5 are satisfied. Once we have that claim chart, we will be in a better position to consider whether there are products representative of groups of products that have the relevant features in common.

# HellerEhrman

William H. Manning June 25, 2008 Page 3

#### IV. U.S. Patent No. 5,545,592

You have asked Samsung to provide evidence that "the process used to manufacture the two exemplar [K4T1G164QA-ZCD5 and K9WAG08U1A] chips is the same, in every material way, as the process used to manufacture Samsung's other DRAM and NAND Flash chips." Again, however, we first need to know from AMD what it considers to be "every material way" in this context. We suggest that you provide us with a claim chart showing how AMD contends the K4T1G164QA-ZCD5 and K9WAG08U1A products infringe claims 1 and 8 of the '592 patent, particularly pointing out how these products are contended to satisfy each of the limitations of those claims. Once we have that chart, we will be in a better position to consider whether there are products representative of groups of Samsung products that have in common the features that AMD believes to be important to its case.

#### V. U.S. Patent No. 5,623,434 and U.S. Patent No. 5,377,200

It is our understanding from your letter that AMD is asserting these patents against the circuitry of the ARM cores contained in various Samsung products. Accordingly, we are willing to consider providing you with a list of which Samsung products incorporate which of the ARM cores that you have listed. We would also consider agreeing to a representative product containing each pertinent type of ARM core, provided that the parties agree that the '434 and '200 patents are being asserted against circuitry that is solely contained with the ARM core, and not against any circuitry outside of the ARM core. Obviously, if circuitry outside of the ARM core is implicated in any way, it will be much more difficult to agree on representative products.

Finally, with respect to both of these patents, you have stated that an agreement as to representative products containing ARM cores "will not eliminate AMD's need for discovery to determine whether Samsung's proprietary semiconductor parts also practice the . . . patent claims." Unless you have some evidence, however, that any Samsung product not incorporating an ARM core infringes any of the claims of these two patents, we do not believe that you have the necessary basis to pursue an infringement claim against such products, under Rule 11. Obviously, if you do have such evidence, please let us know.

#### VI. U.S. Patent No. 6,784,879

You have proposed that Samsung identify the groups of televisions, camcorders, and cell phones that incorporate "the same or similar user interface" as the television, camcorder, and cell phone that AMD has identified. In order to do as you propose, however, we need to know what it is about that user interface that AMD believes infringes the '879 patent. Although you have noted the picture-in-picture aspect of certain Samsung televisions, you have not told us what it is about the picture-in-picture feature that allegedly infringes the '879 patent. Furthermore, as camcorders and cell phones generally do not have a picture-in-

# HellerEhrman

William H. Manning June 25, 2008 Page 4

picture features, we do not know what it is about the user interfaces of those products that AMD is accusing of infringement.

We propose that AMD provide us with a claim chart showing how the particular television, camcorder, and cell phone identified by AMD are contended to infringe claims 1, 6, 11, 14, 17, and 21 of the '879 patent, particularly pointing out what it is about those products that is contended to infringe each of the limitations of those claims. Once we have that chart, we will be in a better position to consider whether there are groups of products that have the relevant features in common.

\* \* \*

Finally, we note that your letter does not state whether AMD is also interested in identifying representative AMD products accused of infringement by Samsung, in order to limit the discovery that will be required of AMD in this case. Please let us know AMD's position on this point.

Very truly yours,

hristine Staskelt

Christine Saunders Haskett

# EXHIBIT C

## ROBINS, KAPLAN, MILLER & CIRESI LLP

2800 LASALLE PLAZA 800 LASALLE AVENUE MINNEAPOLIS, MN 55402-2015 TEL: 612-349-8500 FAX: 612-339-4181 www.rkmc.com

ATTORNEYS AT LAW

WILLIAM H. MANNING 612-349-8461

July 10, 2008

#### VIA FEDERAL EXPRESS

Christine Saunders Haskett, Esq. Heller Ehrman LLP 333 Bush Street San Francisco, CA 94104-2878

#### Re: Advanced Micro Devices, Inc., et al. v. Samsung Electronics Co., Ltd., et al.

Dear Christine:

I write to advance our conversation regarding identifying exemplar Samsung products in order to streamline discovery and trial. I have considered your letter dated June 25, 2008, and believe that AMD can address the concerns you have raised.

As I understand your letter, you have taken the position that for the Cheng '990, Sakamoto '893, Patel '830, Iacoponi '592, and Orr '879 patents, you cannot begin to identify representative Samsung products until AMD provides, for each patent, a claim chart that shows where each claim element is found in an accused product, and the documents that support each chart. We respect your request, and in response I have enclosed with this letter a detailed claim chart for each of those five patents. This detail should allow you to propose an exemplar product for each patent based on the relevant infringing structural and operational features that AMD has identified.

In addition to the claim charts for each patent that you requested, I have also enclosed a set of infringement claim charts based on publicly available information that AMD and its experts have reviewed. This set includes additional infringement claim charts and supporting documents for the five patents mentioned above, as well as charts and supporting documents for the Purcell '434 and Pedneau '200 patents, which you did not request. The charts I have enclosed likely will correspond to the preliminary infringement contentions that AMD will produce to Samsung and the Court on September 30. This set of information should allow you and your client to identify exemplar products for each patent and the other products contained within the groups the exemplars represent. I have enclosed three sets of the charts and supporting documents in both electronic and hard copy for your convenience.

The enclosed charts do not constitute preliminary infringement contentions under the Northern District of California Local Rules, nor do they constitute any kind of discovery

response or any other type of paper or pleading being served in this litigation. Instead, they are informal documents that we are sending for the purpose of identifying product groupings and exemplars. Therefore, AMD will not be bound by these charts and retains the right to change them.

As you can see from the charts and discussion below, it is easily possible to reduce the number of products that will require significant discovery in this case. For example, the number of Samsung products that will require detailed discovery for the Cheng patent should be reduced to 15 to 20 exemplar products. The other six patents will require far fewer exemplar products. The Sakamoto patent should require only one exemplar product, the Patel patent should require only three, and the Iacoponi patent only two. The parties should be able to agree that for the Purcell and Pedneau patents, AMD will need detailed discovery on only exemplar products that contain specific ARM cores—two products for Purcell, and three for Pedneau—along with discovery on agreed-upon exemplars of Samsung proprietary processors. Finally, for the Orr patent, AMD should only need discovery on three exemplar products if Samsung can identify groups of products that employ similar user interfaces. In sum, of the over 15,000 products on the list attached as Exhibit A to Plaintiffs' First Set of Interrogatories, AMD should need detailed infringement discovery for only 40 products.

In order to facilitate mutual cooperation in streamlining this case for discovery and trial, AMD also has taken steps to identify exemplar AMD products that Samsung has accused of infringement. At this point, however, Samsung has given AMD minimal information about Samsung's infringement contention, including what products and structures within those products allegedly infringe which asserted patents. AMD therefore needs Samsung to provide information as AMD has provided with this letter, including infringement claim charts and supporting documentation. AMD can have meaningful conversation about exemplar AMD products only after Samsung provides allegations of infringement that are more detailed than the assertion against "semiconductor devices and/or products incorporating semiconductor devices" in Samsung's Answer and Counterclaims, and a list of "accused products" in Samsung's discovery requests.

The following sections of this letter respond to the patent-specific concerns that you raised in your letter. I believe that this letter and the enclosures provide Samsung more than enough information to identify product groups and representative exemplar products.

#### I. U.S. Patent No. 5,559,990 (Cheng)

Your letter correctly states that AMD believes that most of Samsung's memory products share the operational and structural characteristics that are relevant to the claims of the Cheng '990 patent. These operational and structural characteristics are clearly understood from the patent claims themselves, which define the scope of the Cheng invention and the characteristics necessary to determine both infringement and exemplar categories. However, to provide greater assistance to Samsung to determine which products are representative of groups of products for purposes of discovery and infringement, I have enclosed as Exhibits B-J detailed infringement charts for claims of the Cheng patent. These infringement charts show from publicly available

information the operational and structural characteristics of Samsung memory products which confirm infringement of the Cheng patent.

Your letter also raised questions regarding AMD estimates for the necessary discovery of approximately 15 to 30 Samsung products for purposes of infringement. The chart enclosed as Exhibit A below will assist Samsung in understanding our reasoning behind these numbers and guide Samsung to denoting certain memory products as representative of a larger group of products. The first column of the chart outlines the nine categories of memory which infringe the Cheng patent, as described in our letter of June 10. For each of these categories, the second column lists our current understanding of the Samsung memory chips, by part number, which fall under this category and for which AMD is entitled to collect damages. Obviously, it is Samsung's burden to verify and supplement this list with any missing products, based upon the product list and interrogatories previously provided to Samsung. The third column lists the publicly available datasheet for that product. Samsung's grouping of multiple products being covered with the same datasheet naturally leads to a grouping of products. The number of groups can be consolidated by noting the similarity of structures and characteristics of Samsung memory products within those groups based upon publicly available documentation.

The fourth column sets forth our suggested discovery groupings based on this consolidation. Discovery on these 38 groups of products should allow AMD to further reduce the number of groupings by approximately a factor of two. This reduction will be made based upon studying the relevant technical documentation for these groupings and ascertaining the similar operational and structural characteristics that are not clearly determinable based upon publicly available documentation alone. The end result will be approximately 15-20 exemplar groups for the Cheng patent. AMD is open to discussions with Samsung engineers to further reduce the number of exemplar groups.

#### **II.** U.S. Patent No. 5,248,893 (Sakamoto)

Your letter requests claim charts for Samsung's products containing S-RCAT and RCAT transistors so that Samsung can understand which of its products share the appearance, layering, and composition characteristics that are relevant to infringement of the Sakamoto '893 patent. In particular, Samsung has requested charts for claims 1, 4, and 14. To provide greater assistance to Samsung to determine which products are representative of groups of products for purposes of discovery and infringement, I have enclosed as Exhibit K a detailed claim chart for all claims of the Sakamoto patent that AMD presently intends to assert against Samsung products. This infringement chart shows the operational and structural characteristics of Samsung memory products which indicate infringement of the Sakamoto patent.

The enclosed claim chart contains information about both S-RCAT and RCAT transistors. Based on published Samsung technical papers, we believe that the infringement analysis for the S-RCAT transistors applies equally to Samsung's RCAT technology for all asserted claims of the Sakamoto patent.

#### III. U.S. Patent No. 4,737,830 (Patel)

Your letter requests claim charts for a representative product that infringes claim 5 of the Patel '830 patent. To provide greater assistance to Samsung to determine which products are representative of groups of products for purposes of discovery and infringement, I have enclosed as Exhibit L a detailed claim chart demonstrating how claims 5 and 6 of the Patel patent, which include the limitations of claim 1, read on Samsung's DRAM memory. In addition, AMD has enclosed as Exhibits M-N claim charts for Samsung NAND and SRAM memory. While capacitor layout can vary, we believe that Samsung follows time-tested industry protocol that includes placing capacitors below power busses in memory devices. We believe that Samsung follows similar design practices for other semiconductor products, including processors. This practice should make it easier for Samsung to group products for purposes of infringement and discovery.

#### IV. U.S. Patent No. 5,545,592 (Iacoponi)

Samsung requested claim charts that illustrate how Samsung's K4TIGI64QA-ZCD5 and K9WAG08UIA products infringe claims 1 and 8 of the Iacoponi '592 patent. Enclosed as Exhibits O-P are detailed claim charts for the claims of the Iacoponi patent that AMD presently intends to assert against Samsung. These claim charts specifically identify the layers in Samsung's source/drain contacts that correspond to the claim limitations of the Iacoponi patent. We believe that it will be relatively easy for Samsung to establish product groupings based on the use of these process steps across many Samsung product lines.

#### V. U.S. Patent No. 5,623,434 (Purcell) and U.S. Patent No. 5,377,200 (Pedneau)

You have suggested that Samsung will consider providing a list of products that incorporate the ARM processor cores identified in my June 10, 2008 letter. We believe that such a list will substantially advance the goal of identifying exemplar products that AMD accused of infringing the Purcell and Pedneau patents. We therefore request that Samsung provide that list as soon as possible. I have enclosed as Exhibits Q-R claim charts that demonstrate infringement of Purcell by ARM7TDMI and ARM9TDMI products, and have enclosed as Exhibits S-U claim charts that demonstrate infringement of Pedneau by ARM7EJ-S, ARM9EJ-S, and ARM9E-S products.

You also have suggested that Samsung does not have an obligation to provide discovery regarding Samsung's proprietary processor parts. Case law, however, demonstrates that AMD may obtain discovery on products that are not named specifically in preliminary infringement contentions. *See DR Sys., Inc. v. Fujifilm Med. Sys. USA, Inc.*, No. 06cv417 JLS (NLS), 2008 WL 1734241, at \*3 (S.D. Cal. Apr. 10, 2008) (allowing discovery on products not named in infringement contentions); *LG Elecs. Inc. v. Q-lity Computer Inc.*, 211 F.R.D. 360, 368 (N.D. Cal. 2002) (showing that judges do not limit discovery to products named in infringement contentions); *O2 Micro Int'l Ltd. v. Monolithic Power Sys., Inc.*, 467 F.3d 1355, 1366 (Fed. Cir. 2006) ("If a local patent rule required the final identification of infringement and invalidity contentions to occur at the outset of the case, shortly after the pleadings were filed and well

before the end of discovery, it might well conflict with the spirit, if not the letter, of the notice pleading and broad discovery regime created by the Federal Rules."). Samsung makes and sells proprietary processors, including the CalmRISC series, for use in microcontrollers and other small parts that would benefit from using the inventions claimed by Purcell and Pedneau. These parts, like ARM cores, are based on reduced instruction set computing architectures. Therefore, information about these proprietary products is relevant and discoverable.

In order to expedite the process of identifying exemplar products for Samsung's proprietary cores, AMD suggests that Samsung review the enclosed claim charts for Purcell and Pedneau and provide AMD with documentation for the relevant features of the architecture used by Samsung's proprietary processor cores. The parties can then develop an agreement about exemplar products for Samsung's proprietary semiconductor parts.

#### VI. U.S. Patent No. 6,784,879 (Orr)

I have enclosed as Exhibits V-X claim charts for the television, digital camcorder, and cell phone that I identified in my June 10 letter. The charts show which features of those products infringe the Orr claims. As you have suggested, you now should have the information needed to identify groups of Samsung consumer electronics that use the same or similar user interfaces as these products.

#### VII. Conclusion

AMD now has responded to all requests you made and issues you raised in your letter on June 25, 2008. The detailed claim charts and supporting documentation enclosed with this letter will give you enough information to propose exemplar products and product groupings. It should easily be possible, if the parties cooperate, to reduce AMD's infringement discovery to a very small subset of the 15,000 products listed in Exhibit A to Plaintiffs' First Set of Interrogatories. That subset may contain only approximately 40 products. Reaching an agreement on these exemplars and the groups they represent will meet your prior request to streamline discovery. When Samsung provides AMD with the same information, in the same level of detail, AMD will unquestionably cooperate to identify exemplar products of its own. We look forward to continuing this discussion.

Sincerely,

ROBINS, KAPLAN, MILLER & CIRESI L.L.P.

Hanning William H. Manning

WHM/arf

cc: Robert T. Haslam, Esq., w/o enclosures (*via email only*) Michael K. Plimack, Esq., w/o enclosures (*via email only*) Alan H. Blankenheimer, Esq., w/o enclosures (*via email only*)

Enclosures:

Banker's boxes, each containing claim charts and supporting documents for all seven patents, and CDs containing the same materials.

# EXHIBIT D

#### Case 3:08-cv-00986-SI Document 73-6 Filed 08/25/2008 Page 2 of 15

#### Advanced Micro Devices, Inc., et al. v. Samsung Electronics Co., Ltd., et al., Case No. CV-08-0986-SI Exhibit K – Sakamoto 5,248,893 – DRAM Infringement Chart

The following sets forth the manner in which the Defendants' (collectively referred to as "Samsung") DRAM products infringe U.S. Patent No. 5,248,893. Plaintiffs allege that all elements are present literally, but reserve the right to allege that any particular element is present by equivalents if Samsung establishes that the element is not present literally.

| Claim | Claim Element Text                                                             | Infringement Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | An insulated gate field effect device comprising:                              | Samsung's DRAMs include insulated gate field effect transistors as set forth below.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1(a)  | a first conductivity type<br>semiconductor substrate<br>having a main surface; | Samsung's DRAMs include a semiconductor substrate of a first conductivity type.<br>The substrate has a main surface. This is shown in the figure below, which<br>consists of a TEM image of a cross section of a transistor from an exemplar<br>Samsung DRAM (K4T51083QE). <sup>1</sup> This figure shows the presence of a<br>semiconductor substrate. The area below the dotted line labeled "Junction" has a<br>first conductivity type. The area of the main surface is labeled on the TEM image. |

<sup>&</sup>lt;sup>1</sup> Plaintiffs' contentions are not limited to the exemplar Samsung DRAM chips depicted herein. Those depictions are for illustrative purposes only. Plaintiffs contend that Samsung's DRAM chips generally infringe, but are unable to identify the precise models without further discovery.

| Claim | Claim Element Text | Infringement Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                    | WSix<br>Poly 1<br>61nm<br>Neck<br>65nm<br>Gate Oxide<br>Junction<br>Sphere<br>Part                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       |                    | The TEM set forth above is from a cross section of a Samsung S-RCAT design.<br>AMD's contentions are not limited to Samsung's DRAMs containing S-RCATs.<br>Samsung's DRAMs containing RCATs also meet this claim element. As set forth<br>in the cross-section SEM image depicted below (taken from Kim et al.,<br>Technology for sub-50nm DRAM and NAND Flash Memory, (2005)), those<br>products have a substrate with a main surface (see area labeled "main surface").<br>The area below the dotted line would be of a first conductivity type. |

| Claim | Claim Element Text                                                                                                                                         | Infringement Support                                                                                                                                                                                                                                                                               |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                            | Main Surface                                                                                                                                                                                                                                                                                       |

| 1(b)  | said semiconductor<br>substrate having a concave<br>surface formed on said<br>main surface extending to a<br>prespecified depth below<br>the main surface; | The semiconductor substrate in Samsung's DRAMs have a concave (i.e., recessed below the main surface) surface that extends from the main surface to a predetermined depth below the surface. This feature is illustrated in the two images reproduced above (see areas labeled "Concave Surface"). |

| 1(c)  | an insulating film formed<br>on said concave surface;                                                                                                      | Samsung's DRAMs include an insulating layer on the concave surface portion.<br>The S-RCAT TEM image set forth above shows the insulating layer in the<br>concave area (see area labeled "Gate Oxide").                                                                                             |

| 1(d)  | a conductive gate electrode<br>formed above said<br>insulating film, overlying                                                                             | Samsung's DRAMs include a conductive gate electrode formed above the insulating film, overlying the concave surface. This is illustrated in the S-RCAT TEM, which is reproduced below with relevant labels (see area labeled "Gate".)                                                              |

| Claim | Claim Element Text                                                                                                                                               | Infringement Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | the concave surface;                                                                                                                                             | The location of this gate shows that it is above the insulating film and overlies the concave surface.                                                                                                                                                                                                                                                                                                                                                                                        |

|       |                                                                                                                                                                  | WSix<br>Poly 1<br>Sinm<br>Neck<br>65nm<br>Action<br>Junction<br>Sphere<br>Part                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1(e)  | first and second impurity<br>regions of a second<br>conductivity type<br>respectively formed in the<br>substrate, in the vicinity of<br>said main surfaces, self | Samsung's DRAMs have first and second impurity regions. They appear in the S-RCAT TEM reproduced below, in the area labeled "Source and Drain Regions." They are formed in the substrate, and are in the vicinity of the main surface because they extend up to the main surface. They are on either sides of the gate and are self-aligned to the gate because two separate masks are not needed to align the gate and the edges of source/drain regions. This is confirmed by the following |

| Claim | Claim Element Text                                                                                         | Infringement Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | aligned to and positioned at<br>one side and the other side<br>of said gate electrode<br>respectively; and | publications: J.Y. Kim et al, S-RCAT (Sphere-shaped- <u>Recess-Channel-Array</u><br><u>Transistor</u> ) Technology for 70nm DRAM Feature Size and Beyond, 2005<br>Symposium on VLSI Technology Digest of Technical Papers; and H.J. Oh et al.,<br>High-Density Low-Power-Operating DRAM Device Adopting 6F <sup>2</sup> Cell Scheme<br>with Novel S-RCAT Structure on 80nm Feature Size and Beyond, Proceedings of<br>ESSDERC, Grenoble, France (2005). These publications describe the process for<br>fabricating S-RCAT transistors. |

|       |                                                                                                            | WSix<br>Poly 1<br>61m<br>Neck<br>65nm<br>Gate Oxide<br>5mm<br>Source and Drain<br>Regions                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1(f)  | A first conductivity type region located in said                                                           | In Samsung's DRAMs, there is a first conductivity type region in the substrate (i.e. the area below the "Junction" in the S-RCAT TEM reproduced above). It is                                                                                                                                                                                                                                                                                                                                                                          |

| Claim | Claim Element Text                                                                                                                                                                                                                                                                                                                                                                                                     | Infringement Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | semiconductor substrate<br>between said first and<br>second impurity regions for<br>defining a channel region<br>and a channel-free region<br>extending conformably<br>under and along said<br>concave surface                                                                                                                                                                                                         | between the source and drain regions because it extends from one to the other.<br>The channel region and the channel free region forms in the first impurity region<br>under and along the gate oxide that extends under the portion of the gate labeled<br>"Sphere Part" in the TEM reproduced above.                                                                                                                                                                                                                        |

| 1(g)  | wherein the depth of said<br>concave surface is set to a<br>value which ranges between<br>one and two times the depth<br>of said first and second<br>impurity regions, and                                                                                                                                                                                                                                             | It is readily apparent in the S-RCAT TEM reproduced above that depth of the concave surface is between one and two times the depth of the source/drain.                                                                                                                                                                                                                                                                                                                                                                       |

| 1(h)  | wherein the concave surface<br>is continuously curved in<br>the vicinity of at least one<br>of the first and second<br>impurity regions to produce<br>smooth merger of a<br>conforming first depletion<br>region formed around the at<br>least one impurity region<br>and a conforming second<br>depletion region formed in<br>the vicinity of the gate<br>electrode so that excessive<br>field concentration will not | In Samsung's DRAMs, the concave surface is continuously curved in the area just<br>below the area labeled "junction" in the S-RCAT TEM depicted above, which is<br>where the first and second impurity regions (i.e. the source/drain regions) exist.<br>By virtue of this shape, the depletion region formed around the gate and the<br>depletion regions formed around the impurity regions would merge together in a<br>smooth way. As a result, excessive field concentration would not develop in the<br>area of merger. |

| Claim | Claim Element Text                                                              | Infringement Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |